# Secure Resource Sharing for Embedded Protected Module Architectures

Jo Van Bulck

Thesis voorgedragen tot het behalen van de graad van Master of Science in de ingenieurswetenschappen: computerwetenschappen, hoofdspecialisatie Veilige software

#### **Promotor:**

Prof. dr. ir. Frank Piessens

#### Assessoren:

Dr. ir. C. Huygens Dr. J. Sneyers

#### **Begeleiders:**

Ir. J. Noorman Dr. J.T. Mühlberg

#### © Copyright KU Leuven

Without written permission of the thesis supervisor and the author it is forbidden to reproduce or adapt in any form or by any means any part of this publication. Requests for obtaining the right to reproduce or utilize parts of this publication should be addressed to the Departement Computerwetenschappen, Celestijnenlaan 200A bus 2402, B-3001 Heverlee, +32-16-327700 or by email info@cs.kuleuven.be.

A written permission of the thesis supervisor is also required to use the methods, products, schematics and programs described in this work for industrial or commercial use, and for submitting this publication in scientific contests.

Zonder voorafgaande schriftelijke toestemming van zowel de promotor als de auteur is overnemen, kopiëren, gebruiken of realiseren van deze uitgave of gedeelten ervan verboden. Voor aanvragen tot of informatie i.v.m. het overnemen en/of gebruik en/of realisatie van gedeelten uit deze publicatie, wend u tot het Departement Computerwetenschappen, Celestijnenlaan 200A bus 2402, B-3001 Heverlee, +32-16-327700 of via e-mail info@cs.kuleuven.be.

Voorafgaande schriftelijke toestemming van de promotor is eveneens vereist voor het aanwenden van de in deze masterproef beschreven (originele) methoden, producten, schakelingen en programma's voor industrieel of commercieel nut en voor de inzending van deze publicatie ter deelname aan wetenschappelijke prijzen of wedstrijden.

# **Preface**

Before jumping to protected module architectures and secure resource sharing, this is the time to thank some people who have helped me along the way. First off, I would like to thank my advisers Job Noorman and Jan Tobias Mühlberg for their continuous support, guidance, and for all the things they have learned me over the past year. Without our weekly meetings, this thesis would certainly have been less fun. My thanks also goes to my promoter prof. Piessens for allowing me to work on an initially rather vague thesis topic. Furthermore, I would like to thank my family and friends for their encouragements and for listening to my way to long elaborations on the thesis subject. I am also grateful to the reader for taking the time to review my work.

My special thanks goes to the entire open source community for believing in an ideal and for providing the tools without which this thesis would simply be unimaginable. As a final acknowledgement, my thanks goes the following non-exhaustive list of architects for making the world more beautiful and a thesis less severe: Aldo Van Eyck, Álvaro Siza, Bernard Tschumi, Charles & Ray Eames, Charlotte Perriand, Frank Gehry, Gerrit Rietveld, Le Corbusier, Marcel Breuer, Rem Koolhaas, Superstudio, and Walter Gropius.

Jo Van Bulck

# Contents

| Pr | reface                                                                                                                                                         | i                          |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Al | bstract                                                                                                                                                        | iv                         |

| Sa | amenvatting                                                                                                                                                    | $\mathbf{v}$               |

| Li | st of Figures and Tables                                                                                                                                       | vi                         |

| Li | st of Abbreviations and Symbols                                                                                                                                | vii                        |

| 1  | Introduction  1.1 Protected Module Architectures                                                                                                               | 1<br>1<br>2<br>3           |

| 2  | Background2.1 Conventional Software Isolation2.2 Protected Module Architectures2.3 Conclusion                                                                  | 5<br>5<br>9<br>14          |

| 3  | Embedded Protected Module Architectures 3.1 Sancus                                                                                                             | 15<br>15<br>23<br>25<br>28 |

| 4  | Logical File Access Control  4.1 Motivation 4.2 Design and Implementation of a Protected File System 4.3 Experimental Evaluation 4.4 Discussion 4.5 Conclusion | 29<br>31<br>35<br>39<br>45 |

| 5  | Secure Scheduling 5.1 Threading in a Protected Single-Address-Space                                                                                            | 47<br>49<br>55<br>62<br>67 |

| 6  | Conclusion                                                                                                                                                     | 69                         |

| С |        |    |   |     |     |              |

|---|--------|----|---|-----|-----|--------------|

|   | $\sim$ | NΤ | т | ותו | NTC | $\mathbf{r}$ |

|   |        |    |   |     |     |              |

|   |        |    |   |     |     |              |

|              | 6.1 Limitations and Challenges | 70         |

|--------------|--------------------------------|------------|

| A            | Complete Threading Example     | <b>7</b> 5 |

| В            | Paper First Semester           | <b>7</b> 9 |

| $\mathbf{C}$ | Paper Second Semester          | 91         |

| Bi           | bliography                     | 109        |

## Abstract

Small embedded devices are becoming omnipresent in our daily lives. Through the rise of wireless sensor networks, ubiquitous computing and the Internet of Things, lightweight extensible platforms are increasingly entrusted critical and privacy-sensitive tasks. Yet, to minimise production costs and power consumption, these devices commonly lack hardware support for conventional security measures, such as virtual memory and processor privilege levels.

In this respect, recent research on hardware-level Protected Module Architectures (PMAs) provides an alternative, very lightweight memory protection scheme. These systems allow the execution of security-critical code in protected modules that are isolated from the rest of the system, without relying on a trusted software layer to enforce this separation. While secluding software modules in their own hardware-enforced protection domains allows for strong security guarantees, it also limits their ability to securely share platform resources, such as CPU time or peripheral devices.

This master's thesis explores the feasibility of supplementing the hardware-enforced security guarantees offered by the Sancus PMA with availability and access control guarantees for shared system resources. In contrast to a conventional Operating System (OS), an omnipotent kernel software layer is not introduced. The main contributions of this master's thesis are twofold. First, a generic approach to encapsulate and control access to a shared platform resource is proposed. The approach is implemented and evaluated for a protected file system that can control access to either a shared memory buffer or a shared peripheral flash drive. Second, a secure multithreading model and an accompanying unprivileged scheduler implementation are presented. The scheduler controls access to the CPU time resource by interweaving the execution of logical threads that are conceptually isolated from each other and that might span multiple protection domains.

The work presented in this master's thesis shows that embedded PMAs provide sufficiently strong hardware primitives to not only isolate software modules from each other, but also allow secure implementation of typical OS responsibilities.

# Samenvatting

Geïntegreerde computersystemen worden steeds meer alomtegenwoordig in ons dagelijkse leven. Zo worden kleine, uitbreidbare computers steeds vaker ingezet voor kritische en privacygevoelige taken. Echter, omwille van de kostprijs en het stroomverbruik, zijn deze apparaten doorgaans sterk beperkt in hardware-ondersteuning voor gevestigde beveiligingsmaatregelen, zoals virtueel geheugen en beveiligingsringen voor processors.

Recent onderzoek naar geïntegreerde beveiligingsarchitecturen stelt alternatieve lichtgewicht geheugenbescherming voor. Daarbij is het mogelijk kritische code in geïsoleerde, beschermde modules uit te voeren, zonder op software te moeten vertrouwen die deze afzondering afdwingt. Software modules op deze manier in hardware afzonderen laat zeer sterke beveiligingsgaranties toe. Anderzijds biedt het beperkte ondersteuning voor het veilig delen van systeembronnen, bijvoorbeeld processortijd of randapparaten.

Deze masterscriptie onderzoekt de haalbaarheid van het aanvullen van beveiligingsgaranties die worden afgedwongen door de hardware met beschikbaarheidsen toegangscontrolegaranties voor gedeelde systeembronnen. In tegenstelling tot een traditioneel besturingssysteem wordt een almachtige kernel softwarelaag niet geïntroduceerd. De belangrijkste bijdragen van deze thesis zijn tweevoudig. Ten eerste stelt deze thesis een algemene aanpak voor om een systeembron te encapsuleren en de toegang ertoe te controleren. Deze aanpak wordt geïmplementeerd en geëvalueerd voor een beschermd bestandssysteem dat de toegang kan controleren tot ofwel een gedeelde interne geheugenbuffer, ofwel een gedeeld extern flashgeheugen. Ten tweede stelt deze thesis een veilig multitasking model en een bijhorende nietbevoorrechte scheduler voor. De scheduler controleert toegang tot de processortijd door de uitvoering van logische uitvoeringsthreads te verweven. Deze logische threads zijn conceptueel geïsoleerd van elkaar en kunnen meerdere beschermde modules omvatten.

Het werk gepresenteerd in deze masterproef toont aan dat geïntegreerde beveiligingsarchitecturen voldoende krachtige hardware primitieven bieden om niet alleen software modules van elkaar scheiden, maar ook om veilige besturingssysteemconcepten te implementeren.

# List of Figures and Tables

### List of Figures

| 2.1<br>2.2 | Microkernel architecture with server processes in user space Protected software module layout in the shared address space | 7<br>10              |

|------------|---------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.1        | Layout of a Sancus module and protected storage area                                                                      | 18                   |

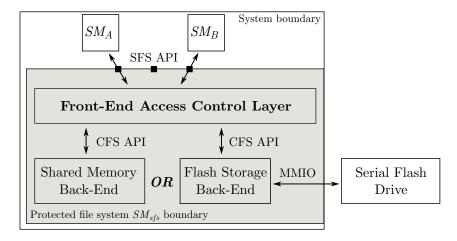

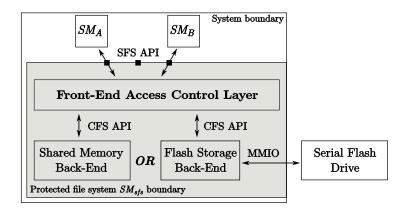

| 4.1        | Layered design of the protected file system module                                                                        | 32                   |

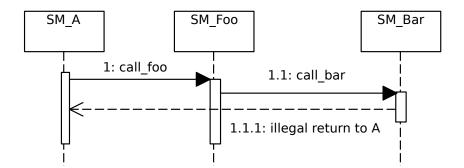

|            | Abuse of an open return entry point                                                                                       | 53<br>57<br>62<br>78 |

| 2.1        | Program counter based access control rules for an SPM                                                                     | 10                   |

| 3.1        | Overview of Sancus' extended instruction set                                                                              | 21                   |

| 4.1<br>4.2 | Number of cycles needed for $SM_{sfs}$ with a dummy back-end Overhead for a client of $SM_{sfs}$ for each back-end        | 37<br>38             |

| <b>5</b> 1 | Overview of the interface offered by the secure scheduler                                                                 | 55                   |

# List of Abbreviations and Symbols

#### Abbreviations

ACL Access Control List

CFS Contiki File System

DoS Denial-of-Service

EA-MPU Execution-Aware Memory Protection Unit

IoT Internet of Things

IPC Inter-Process CommunicationISR Interrupt Service RoutineMAC Message Authentication Code

$\begin{array}{ll} {\rm MAL} & {\rm Memory\ Access\ Logic} \\ {\rm MMIO} & {\rm Memory\hbox{-}Mapped\ I/O} \end{array}$

MMU Memory Management Unit

OS Operating System

PMA Protected Module Architecture

SM Sancus Module

SPM Self-Protecting Module

TCB Trusted Computing Base

TCS Thread Control Structure

#### Symbols

eidx Logical Sancus module entry index

smid Unique identifier for a Sancus module, assigned by the hardware  $SM_{sched}$  Sancus module encapsulating the scheduler implementation  $SM_{sfs}$  Sancus module encapsulating the file system implementation thrid Unique identifier for a Sancus thread, assigned by  $SM_{sched}$

## Chapter 1

### Introduction

Small embedded devices are becoming omnipresent and interconnected in our everyday lives. In an Internet of Things (IoT) where every object is represented by a networked extensible counterpart, adequate software isolation will prove essential to ensure our safety and privacy. Yet, to minimise production costs and power consumption, embedded platforms [17, 20] commonly lack hardware support for established security mechanisms, such as virtual memory and processor privilege levels. Their connectivity and application usages on the other hand make them an interesting target for attackers. It is therefore not surprising that various embedded system security attacks have been described in literature [13, 53, 31, 41].

Due to the lack of lightweight memory isolation techniques, embedded devices generally operate in a *single-address-space* where memory is treated as a global resource, addressable and accessible by everyone. Software running on these devices is thus exposed to modification by malicious or buggy programs. This is especially problematic for reprogrammable devices [21, 10, 15] that feature runtime software extensibility by multiple untrustworthy vendors. As a consequence, recent research on Protected Module Architectures (PMAs) [49, 40, 47, 30] has proposed an alternative memory protection scheme that provides strong, yet inexpensive software isolation for embedded devices. This approach is summarised in Sect. 1.1 and it is explained how current PMAs offer limited support for shared system resources. Section 1.2 thereafter summarises the contributions of this master's thesis that proposes and implements an approach to securely share system resources on embedded PMAs. The structure of the thesis text is outlined in Sect. 1.3.

#### 1.1 Protected Module Architectures

PMAs [49, 47] provide fine-grained memory isolation guarantees in a single-address-space. In short, these architectures allow a programmer to define Self-Protecting Modules (SPMs) with a code and a data section to allow the isolated execution of security-critical code portions. The key characteristic of an SPM is that its private data section is exclusively accessible from its corresponding code section, which can only be entered from a few predefined entry points. An SPM could therefore be

thought of as a standalone enclave in the shared address space. As suggested by its name, a self-protecting module is solely responsible for its own private data section. Attackers from the outside can never directly access the protected data.

PMAs for conventional high-end computer systems have successfully been implemented as an additional layer of protection enforced by a small hypervisor [48] or incorporated in a commodity Operating System (OS) kernel [3]. Hardware-level PMAs [40, 30] on the other hand enforce memory protection through an efficient hardware mechanism [49] that uses the value of the current program counter to decide access to a memory location. As such, hardware-level PMAs can offer an inexpensive, yet substantive memory protection scheme for small embedded devices. Apart from being lightweight, hardware-enforced PMAs are promising because they can isolate SPMs in the shared address space, without relying on any trusted software layer. In this respect, the Trusted Computing Base (TCB) denotes the set of hardware and software components that need to be trusted to ensure the correct execution of a user program. The larger the software part of the TCB, the more likely it contains low-level vulnerabilities that can be exploited using well-known techniques [18] to jeopardise the entire system.

An important advantage of hardware-level PMAs [40, 30] is that they explicitly exclude the OS kernel from the TCB for memory isolation. Confining SPMs in their respective protection domains however also limits their ability to share system resources, such as CPU time or peripheral devices. That is, SPMs should always fulfil their own needs; the only way in which they can get availability or access control guarantees for a platform resource is to claim the resource for themselves. To see how this implies poor flexibility vs. protection guarantees, consider an SPM that denies others access to a peripheral flash drive in order to protect the confidentiality and integrity of its own data, or an SPM that monopolises CPU time to be guaranteed availability at all time. This is evidently undesirable in an embedded context, where system resources are scarce and should be shared among multiple inter-untrustworthy software modules.

#### 1.2 Contributions

This master's thesis explores the possibility of supplementing the hardware-enforced security guarantees offered by embedded PMAs with OS-like availability and access control guarantees for shared system resources. The work of this master's thesis is based upon Sancus [40], a low-cost zero-software PMA explicitly targeted at embedded devices. More specifically, the following contributions are made:

• The minimal set of hardware primitives that need to be provided by a PMA to securely allow the software implementation of OS-like services is identified. An approach to implement OS responsibilities on top of the Sancus architecture is proposed. This approach does not introduce a traditional omnipotent kernel software layer, but rather encapsulates OS concepts in their own unprivileged modules to realise policies not offered by the hardware.

- A generic access control mechanism is proposed to securely share resources

that are being accessed through the memory address space. The approach is

implemented and evaluated for a protected file system that can control access to

either a shared memory buffer, or a peripheral Memory-Mapped I/O (MMIO)

flash drive. The security guarantees and general applicability of the resource

sharing approach are discussed.

- Sancus' existing implicit control flow model is secured by inserting compilergenerated runtime checks at the boundaries of protected modules.

- A multithreading model for Sancus and an accompanying protected scheduler implementation are provided. The approach allows to control access to the more abstract CPU time resource, supplementing the hardware-enforced security guarantees for SPMs with availability guarantees for logical threads. The security and availability guarantees of the prototype are discussed.

The source code of the protected file system and the secure scheduler is publicly available at https://github.com/jovanbulck/thesis-src.

#### 1.3 Outline

The remainder of this text is organised as follows:

- Chapter 2: Background This chapter introduces the relevant software security background for this master's thesis. First, conventional software isolation techniques, their downsides and existing mitigations are discussed. Thereafter, PMAs are introduced as an alternative way of isolating software and a general overview of this recent research area is provided.

- Chapter 3: Embedded Protected Module Architectures This chapter is dedicated to the problem domain of embedded PMAs and formulates the research objectives. First, a detailed overview of Sancus [40], the development platform for this master's thesis, is provided. Sancus is thereafter briefly compared to Trustlite [30], another hardware-level embedded PMA. The final part of this chapter proposes an approach to securely implement OS-like services on top of these architectures. It is explained how this allows to supplement the hardware-enforced security guarantees for protected modules with software-based availability and access control guarantees for shared system resources.

- Chapter 4: Logical File Access Control This chapter presents a protected file system implementation for the Sancus platform. The file system serves as a case study of encapsulating and controlling access to a shared system resource through a lightweight protected software layer on top of hardware-enforced mechanisms. This chapter includes a runtime overhead analysis of the prototype and discuses the security guarantees and general applicability of the resource sharing approach.

#### 1. Introduction

Chapter 5: Secure Scheduling This chapter presents a secure multithreading scheme and accompanying scheduler for the Sancus platform. First, existing ideas and challenges to implement multithreading in a protected single-address-space are reviewed. Thereafter, security improvements to Sancus' existing implicit control flow model are described and a logical threading model and scheduler implementation are provided. The final part of this chapter discusses the security/availability guarantees of the current prototype, compares the approach to other PMAs and elaborates on the possibility of future hardware support for preemption.

**Chapter 6: Conclusion** This chapter concludes the thesis text. The contributions are summarised, limitations are acknowledged and future work directions are provided.

# Chapter 2

# Background

To enforce security guarantees, a computer system should be able to protect the internal state of a running software entity against other potentially malicious entities. This is referred to as *software isolation*. Traditionally, isolating software is a well-known requirement and an active research field. Consequentially, well-understood solutions for commodity high-end computing platforms have been established over the past decades. The recent rise of low-end embedded devices has triggered research for radically new lightweight software protection mechanisms. This chapter aims at providing an overview of conventional as well as novel software isolation techniques. As such this chapter presents the relevant software security background for this master's thesis.

The explanation is organised as follows. Section 2.1 first discusses established isolation techniques and elaborates on how the associated downsides can be mitigated. Section 2.2 thereafter presents Protected Module Architectures (PMAs) as a novel research field that offers a viable alternative to conventional isolation. Finally, Sect. 2.3 formulates a conclusion for this chapter.

#### 2.1 Conventional Software Isolation

On conventional high-end computing devices software isolation is a fundamental requirement that is typically realised by a trusted OS, backed by advanced hardware support. Section 2.1.1 summarises this traditional approach and Sect. 2.1.2 discusses some of its known drawbacks and alternatives. The previous chapter already mentioned that embedded microcontrollers are constrained by economic and power consumption considerations. They therefore commonly lack the hardware resources needed for traditional software isolation. Section 2.1.3 summarises existing ways of isolating software on these devices.

#### 2.1.1 Operating System Isolation

Conventional computer systems [4, 46, 50] rely on hardware support for processor privilege levels and virtual memory to enforce isolation for the OS and between

different applications. Virtual memory techniques introduce a level of indirection between the (virtual) addresses used by programs and the actual locations in physical memory. A dedicated Memory Management Unit (MMU) hardware component is responsible to automate the virtual-to-physical address mapping. Paged virtual memory, the most widely used set-up, stores the virtual-to-physical translation data in an in-memory page table and supplements the MMU with a translation look-aside buffer to speed up subsequent memory accesses.

Conventional OSs allocate a separate page table per process and update an MMU register that points to the current in-memory page table on context switch. Confining processes in private virtual address spaces has two main advantages. First, each process has the entire virtual address space at its disposal. Processes should therefore not worry about the size and current usage of physical memory. Second, private virtual address spaces provide memory isolation between processes. Indeed, since each process has its own virtual-to-physical address mapping, process A cannot access the physical memory assigned to process B (unless such a mapping is explicitly created to realise shared memory).

Memory protection guarantees via private address spaces of course only hold if user programs are prevented from compromising the OS, or from changing the page table themselves. Conventional computer systems therefore rely on hardware-enforced processor privilege levels, also called protection rings, that allow the OS kernel to run more privileged. Regular user programs can request services from the privileged OS through system calls. Such a system call generates a hardware trap that switches to privileged mode and starts executing the appropriate kernel code.

#### 2.1.2 Issues with Conventional Isolation

The above traditional way of isolating software has several well-known drawbacks and researchers have been trying to mitigate them for decades. The following summarises the major drawbacks and proposed alternatives.

#### Trusted Computing Base

The above way of isolating software relies on a layered design where user programs trust and rely on the services of the kernel software layer. This implies that a single vulnerability or bug in the omnipotent kernel jeopardises the entire system, as demonstrated by kernel-level malware. In this respect, the TCB denotes the set of hardware and software components that need to be trusted to ensure the safe execution of a software program. The privileged OS kernel software layer thus belongs to the TCB of any user program. This is problematic from a security perspective for two reasons. First, commodity OS kernels are typically written in an unsafe language such as C. This makes them vulnerable to well-known low-level software attacks [18]. Second, commodity OS kernels consist of millions of lines of code<sup>1</sup>,

<sup>&</sup>lt;sup>1</sup>To give an indication of the size and complexity involved: version 3.18 of the Linux kernel consists of almost 19 million lines of code [12] and Microsoft's Windows XP allegedly contains 45 million lines of code [37].

which makes it practically impossible to secure them against these attacks. The large size results from their monolithic architecture. That is, most OSs implement all services – scheduling, memory management, file systems, device drivers, etc. – in a single kernel program.

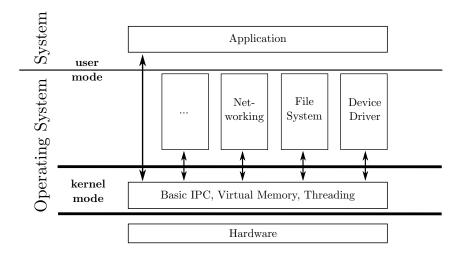

As a response, the *microkernel* architecture [33, 34, 50], depicted in Fig. 2.1, limits the TCB by reducing the size of the trusted kernel layer. The key idea of a microkernel is to implement all non-essential OS services as regular user programs, referred to as *servers*. User programs and servers always communicate indirectly through the microkernel. The privileged microkernel is therefore solely responsible to separate user processes and to provide Inter-Process Communication (IPC) between them. The actual OS services are implemented in user space on top of these abstractions. While microkernels are superior from a security perspective, they have never gained ground in commodity OSs – due to a variety of reasons, including complexity and initial performance issues [34].

FIGURE 2.1: Microkernel architecture with server processes in user space

The TCB consequences of a layered monolithic architecture can also be mitigated by enforcing a modular design. Witchel et al. [54] employ a combination of hardware and software techniques, known as Mondriaan memory protection, to enforce memory isolation of Linux kernel modules. Their approach prohibits a kernel module from accessing another module's memory directly. A vulnerability in one such module (e.g. a device driver) does therefore not jeopardise the entire monolithic kernel program.

Apart from reducing the kernel's size, another strategy to increase its trustworthiness is by formally verifying parts of it. Research on formal verification [43, 38] has indeed proven memory safety of parts of the Linux kernel. While completely verifying a large monolithic kernel such as Linux is infeasible, the functional correctness of the seL4 microkernel implementation has been entirely verified [28]. From a security perspective, such a verified OS kernel remains part of the TCB, but becomes trustworthy. That is, applications that build upon the kernel are provided with strong formalised assurances, as opposed to the implicit entangled TCB of legacy OSs.

#### **Coarse-Grained Protection**

In a conventional OS that provides software isolation via private address spaces, the process as the unit of multiprogramming coincides with the unit of memory protection. In the context of increasingly complex, extensible and object oriented applications however, one could argue that this unit is too coarse-grained. A 1994 paper already addresses the problem: "private-address-space systems force poor tradeoffs between protection, performance, and integration. [...] applications need better control of protection and sharing than current systems can provide." [9].

A private virtual address space per process is needed to be able to re-use virtual addresses in restricted address spaces ( $\leq$  32 bit). The rise of wide-address (64 bit) architectures in the early nineties however rendered this use of private address spaces superfluous. As a result, researchers [8, 9] devised single-address-space OSs that place all processes in a single global virtual address space and realise alternative fine-grained protection domains on top. All programs execute in the same address space, but their memory access rights within this shared address space are determined by their current protection domain. As such, single-address-space OSs separate addressability from accessibility.

Capability-based systems represent another approach to provide fine-grained memory access control in a shared address space. While capability-based systems are an historical [7] research direction, they are currently reviving. The recent CHERI [55] system features a hardware-based capability implementation that offers fine-grained protection domains inside the virtual address space of a conventional OS process. Access rights for memory blocks are represented by *capabilities* and an executing program is granted access to all memory that is described by its current set of capabilities. A capability can be thought of as an unforgeable memory pointer that is specially tagged and that includes additional meta data, such as an offset and permission fields. Capabilities describe access rights to a memory block and are themselves stored in memory. A program that holds a capability is therefore granted access to the corresponding memory block, which may contain other capabilities to extend the memory access rights once more. To prevent applications from defining their own memory access rights, valid capabilities include a special tag that can only be set by a privileged OS kernel [7] or through special hardware instructions [55]. Since capabilities can be passed freely along, or used to create more restrictive capabilities, capability-based addressing simplifies sharing, but makes revocation of previously assigned access rights more difficult.

#### 2.1.3 Embedded Software Isolation

Due the limited resources and specialised needs of embedded devices, a heterogeneous range of small dedicated OSs [20, 56, 17] has emerged in recent years. Initially, these OSs assumed a single, static application. Hence, no need for memory protection: the embedded application was statically linked with the OS into a single monolithic image, sharing an unprotected single-address-space [20]. While embedded OSs nowadays commonly feature concurrency and dynamic reprogramming to update or install

new applications at run time [21, 10, 15], support for memory protection is non-existing or remains very limited. The reason is that resource-constrained embedded microcontrollers generally lack hardware support for established security mechanisms, such as virtual memory and CPU privilege levels. Several authors [17, 21, 24] foretell that these hardware constraints will endure, due to low-power requirements.

Considerable research effort has been put in providing software isolation and OS protection for embedded microcontrollers that lack related hardware support. Safe TinyOS [11] provides efficient type and memory safety by modifying code at compile time. t-Kernel [24] on the other hand provides virtual memory, preemptive scheduling and OS protection by modifying untrusted application code at load time. Both approaches decrease performance and rely on a software TCB to enforce memory protection. The next section introduces a novel hardware memory protection mechanism suitable for efficient runtime memory access control on small devices.

#### 2.2 Protected Module Architectures

The above discussion introduced several issues concerning the way software isolation is traditionally realised. Consequently, recent research on Protected Module Architectures (PMAs) [49, 47] attempts to realise fine-grained memory protection guarantees with a moderate-sized TCB. In short, these architectures allow a programmer to define standalone modules with a code and data section so that security-critical code fragments can be executed in their own protection domain, isolated from the rest of the system.

The explanation is organised as follows. Section 2.2.1 first introduces the concept of a protected software module. Section 2.2.2 thereafter elaborates on the provided security guarantees and Sect. 2.2.3 finally provides an overview of the existing PMA implementations.

#### 2.2.1 Self-Protecting Modules

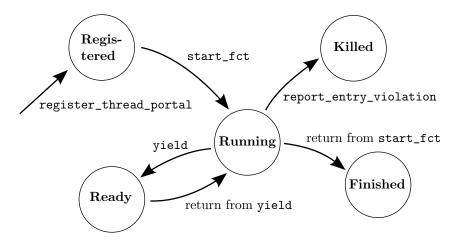

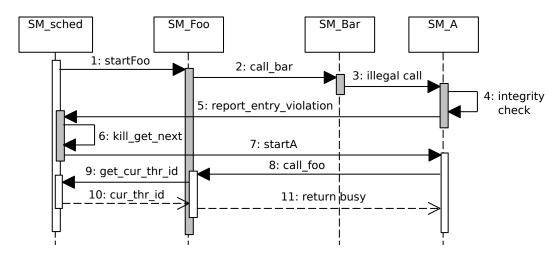

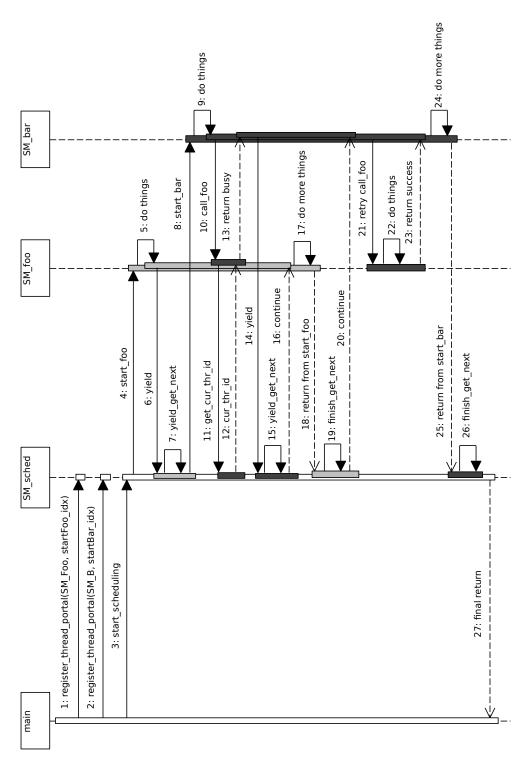

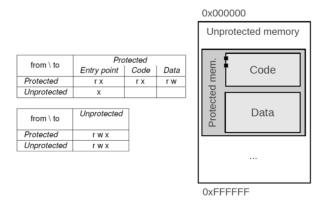

A Self-Protecting Module (SPM) corresponds to a fine-grained protection domain in a shared address space. The layout of an SPM is depicted in Fig. 2.2 and consists of two contiguous memory sections: a public text or code section containing a fixed number of entry points and a private data section. The key characteristic is that an SPM's private data section is exclusively managed by its corresponding code section, which is only entered from a few predefined entry points. An SPM could therefore be thought of as a standalone enclave in unprotected memory. Attackers from outside can never directly access the protected data; a self-protecting module is solely responsible for its own private data section, hence its name.

The concept of SPMs is of course only useful if it can be enforced in a reliable and efficient way. In this respect, program counter based access control [49] is a novel lightweight memory protection technique that uses the current value of the program counter to decide access to a memory location. An SPM can be unambiguously defined in the single-address-space through simple program counter based access control rules in an access control matrix. Table 2.1 lists such memory access rights

FIGURE 2.2: Layout of a protected module  $SPM_A$  in the shared address space (gray areas represent protected memory and black squares represent entry points)

for an SPM in the traditional UNIX notation. All memory addresses are categorised as either "protected", that is belonging to the SPM, or "unprotected". Protected memory is further subdivided as belonging to an entry point, a code section or a data section. The columns of the table categorise the memory location being accessed, whereas the rows categorise the current value of the program counter. Note that when deciding access to an SPM the program counter is only categorised as "protected" when corresponding to an address within the code section of the *same* module (i.e. any other module is treated as if it where unprotected). The program counter based rules in Table 2.1 thus enforce that (i) the code section of an SPM is read-only, (ii) program flow only enters an SPM through one of its predefined entry points, and (iii) the data section of an SPM is only accessible when executing in its corresponding code section.

Table 2.1: Program counter based access control rules for an SPM

| From \ to               | Protected Entry Code Data |      | Unprotected |     |

|-------------------------|---------------------------|------|-------------|-----|

|                         | Entry                     | Code | Data        |     |

| Protected               | r-x                       | r-x  | rw-         | rwx |

| Unprotected / other SPM | r-x                       | r-   |             | rwx |

#### 2.2.2 Security Guarantees

SPMs are realised by a Protected Module Architecture (PMA) implementation, as discussed in the next section. Such a PMA typically provides SPMs with the following security guarantees.

Secure Control Flow As explained above, the code section of an SPM can only be entered via a few predefined entry points. That is, an attacker cannot jump to arbitrary code in the SPM. This prevents him from abusing useful code snippets [45] that operate on private data or from bypassing security-sensitive code (such as access control or encryption functionality). Furthermore, SPMs should maintain their own private call stack to save i.a. function return addresses. Such a safe stack, as initially proposed by Kumar et al. [32] and formalised by Agten et al. [2], ensures that control flow within an SPM protection domain cannot be influenced from outside.

Secrecy of Private Data SPMs are provided with exclusive read and write access to their private data section. This allows a programmer to implement for example a cryptographic module that saves the secret key in its private data section and safely offers encryption/decryption facilities towards others. Such an SPM remains responsible however for the correct implementation of its code section. More specifically, to ensure confidentiality and integrity of the private data section, the corresponding code section should not leak private data and should not be vulnerable to low-level security attacks [18] such as buffer overflows that might tamper with the private data or alter control flow within an SPM. Consequently, the TCB of an SPM consists of (i) the TCB needed to realise the PMA implementation that enforces the SPM's access rights, and (ii) the SPM's own code section.

Authentication To build flexible trustworthy systems, reliable authentication of running SPMs is essential. To do so, support from the PMA implementation is needed. The exact authentication mechanism and guarantees therefore depend on the specific PMA [49, 40, 48, 30]. In general however, to unambiguously identify a running SPM, one minimally needs (i) a cryptographic hash of the code section, and (ii) the exact load addresses of the code and data sections (since the content of the relocatable code section depends on it). Once provided with this information, a cryptographic hash of the publicly readable code section can be calculated and compared to authenticate the identity of the running SPM. For reliable authentication however, one still needs a guarantee that the SPM being verified is still loaded and protected correctly. Such a guarantee should be provided by the supporting PMA's interface, as explained further on.

How exactly the above information is provided depends on the PMA implementation. Strackx et al. [49, 48] for example propose to accompany each SPM with a security report that contains i.a. the memory layout and a cryptographic hash of the code section. Since the security report is signed with the private key of the issuer, SPMs can verify the trustworthiness of the report through a chain of trust to a known certificate authority. Noorman et al. [40] avoid the use of public key cryptography by deploying the calling SPM with a Message Authentication Code (MAC) of the code section and load addresses of the callee.

Secure Communication Strackx et al. [49] show how to set up a secure local communication channel between SPMs that ensures mutual authentication, confidentiality and integrity of the passed data. Their approach relies on reliable SPM authentication and assumes the absence of interrupts. A one-way authenticated channel is set up as follows. First, the calling SPM authenticates the SPM being called. Next, the caller jumps to the callee's desired entry point, passing any arguments safely through CPU registers. Finally, the callee returns to the caller. To do so however, the callee needs the return address. Recall that SPMs have their own private call stack and can only be entered from a few predefined entry points. This implies that (i) the calling SPM should pass the return address as an argument, and (ii) this continuation point cannot simply be the address following the call instruction. Strackx et al. [49] therefore propose to pass the address of a special

return entry point in the calling SPM that restores the internal private call stack and continues internal execution after the call instruction. Moreover, the callee can use the provided address of this entry point to identify and verify the calling SPM, resulting in a mutually authenticated communication channel for return values.

Note that confidentiality and integrity of the passed data is guaranteed because the caller places them in CPU registers before executing an unconditional jump to the callee. This implies that – in the absence of interrupt – only the caller and the callee can see or modify the data. Passing data via CPU registers of course limits the number and size of the arguments. To overcome these limitations, multiple subsequent calls may be used or data can be passed through unprotected memory in encrypted form.

#### 2.2.3 Implementations

As mentioned above, the security guarantees for SPMs should be implemented by a Protected Module Architecture (PMA). Such a PMA can be realised on different levels, depending on the application scenario. This section discusses PMA implementations in hardware, through a trusted hypervisor and incorporated in a trusted OS kernel. Each of these implementations has its own advantages in terms of performance, cost and portability. Moreover, since the PMA enforces the access control rights for SPMs, it is naturally incorporated in the TCB. The choice of the implementation level therefore also defines the size of the TCB.

#### Hardware-Level Implementation

Hardware-level PMAs implement some form of program counter based access control in hardware and extend the instruction set to allow the safe creation of SPMs in the shared address space. The prime advantage of these PMAs is that they feature a small hardware-only TCB. SPMs in these systems indeed rely solely on the correct functioning of the hardware for their security guarantees. Moreover, the modified memory access semantics can be enforced efficiently through a lightweight program counter based access control hardware mechanism that does not increase the memory access time [40, 30]. One of the downsides of a custom hardware implementation however, is that portability of legacy applications is obviously hindered.

Recall from Sect. 2.1.3 that embedded platforms commonly lack hardware support for virtual memory and therefore need an alternative low-cost software isolation scheme. In this context, hardware-only PMAs look particularly interesting as they provide a lightweight, yet substantive memory protection mechanism. Strackx et al. [49] first proposed the general idea of SPMs and program counter based access control as an efficient memory isolation technique for embedded devices. Noorman et al. [40] presented Sancus, a hardware-only PMA explicitly targeted at small embedded devices and the development platform for this master's thesis. Koeberl et al. [30] presented Trustlite, a hardware-enforced PMA that features an execution-aware memory protection unit for small computing devices. Given the importance of the

embedded PMA research field for this master's thesis, a detailed explanation of the Sancus platform and a comparison to Trustlite are presented in Chapter 3.

The recently proposed Intel Software Guard Extensions (SGX) [36, 27] represent a different research direction that employs a hardware-level PMA. In contrast to the embedded approach above, SGX is a set of hardware extensions for high-end multiple-address-space PCs and servers. SGX does not consider program counter based access control as a standalone memory protection mechanism, but rather as a means to complement the existing coarse-grained virtual memory protection scheme. SGX thus allows for hardware-enforced security guarantees in a conventional high-end untrusted execution environment. To this end, SGX extends the Intel architecture with new instructions that allow the creation, destruction, entering and exiting of hardware-protected enclaves within an application's private virtual address space. SGX's hardware model allows a conventional OS to take care of virtual memory translation and swapping of enclave pages, but regards such an OS as an untrusted agent. Furthermore, SGX enclaves feature multiple internal control flow threads that can be interrupted at any time, as discussed in more detail in Sect. 5.1.3.

#### Hypervisor-Level Implementation

The Fides system [48] represents another way of implementing PMAs through a small hypervisor software layer that isolates SPMs in a separate secure virtual machine. Such a hypervisor-level implementation has the advantage that it does not require changing the hardware, at the cost of only a moderate-sized TCB. Fides allows a programmer to define seamlessly integrated SPMs within an application's virtual address space. Fides therefore demonstrates the feasibility of realising PMAs while remaining compatible with legacy hardware and OSs.

The Fides architecture consists of an omnipotent hypervisor bottom layer that keeps track of two separate virtual machines, one for the legacy OS and one for a security kernel that manages SPMs. Both virtual machines have the same view on physical memory, but the hypervisor enforces different access rights. It makes sure that the memory belonging to an SPM cannot be accessed by the legacy OS. The hypervisor thus enforces coarse-grained memory protection guarantees, whereas the fine-grained SPM access control model is enforced by a small dedicated security kernel. As such, secure SPM execution relies on the hypervisor implementation as well as the security kernel, which together represent a relatively small TCB of 7,159 lines of code [48].

The key advantages of the Fides architecture are its compatibility with legacy hardware and software and the fact that the legacy OS is excluded from the TCB for secure SPM execution. Moreover, the performance penalty is acceptable since the hypervisor only needs to switch the virtual machines when entering or exiting an SPM. The Fides architecture inevitably depends on hardware support for processor privilege levels and virtual memory however. This makes a hypervisor-level solution unsuitable for embedded devices.

#### **Kernel-Level Implementation**

The Salus system [3] provides a PMA implementation by extending the Linux kernel. Salus employs SPMs as an additional fine-grained layer of protection inside the virtual private address space of a Linux process. Recall from Sect. 2.1.2 that an application programmer in a conventional multiple-address-space OS environment is obligated to compromise between protection and performance. The key advantage of Salus is therefore that it allows a single process to consist of multiple logical protection domains where a vulnerability in one SPM cannot affect the others. To this end, Salus also includes a privilege containment mechanism to limit the system calls that can be used by a specific SPM.

While such an implementation is interesting from a pragmatic point of view, it also enlarges the TCB. In contrast to the above PMAs, Salus does not execute SPMs in an isolated part of the system. A single vulnerability in the omnipotent monolithic kernel layer indeed suffices to invalidate the security guarantees for SPMs. Moreover, a kernel-level implementation inevitably relies on hardware-support for processor privilege levels and is therefore unsuitable for embedded devices.

#### 2.3 Conclusion

Adequate software isolation through memory protection is imperative to enforce security guarantees for a shared computing platform. Well-understood protection mechanisms have been established for classical computer systems. The most widespread approach isolates processes in their own private virtual address space through a trusted OS that is shielded from the applications. Important well-known disadvantages of such an approach include (i) a large TCB that incorporates the OS kernel, and (ii) the lack of additional fine-grained protection domains inside the virtual address space of a process. Moreover, the approach inevitably relies on hardware support, which is not widely available for embedded systems – to minimise production costs, as well as power consumption.

Consequentially, recent research on PMAs attempts to provide inexpensive and fine-grained protection domains in a shared address space, while keeping the TCB small. This chapter discussed PMAs that allow hardening security critical applications on conventional high-end computers, but also mentioned lightweight hardware-level PMAs that can offer a standalone substantive memory protection model for low-end embedded devices. The next chapter elaborates further on embedded hardware-level PMAs and the consequences of a zero-software TCB that excludes the OS kernel.

# Chapter 3

# Embedded Protected Module Architectures

The previous chapter introduced the general research area on PMAs and their relevance in an embedded context. Since this master's thesis builds upon Sancus, a hardware-enforced PMA for small embedded devices, this chapter is entirely dedicated to the problem domain of embedded hardware-level PMAs and formulates the research objectives.

The chapter is organised as follows. Section 3.1 first provides a detailed description of Sancus, the development platform for this master's thesis. Next, Sect. 3.2 briefly contrasts the Sancus architecture with Trustlite, a similar embedded hardware-level PMA with a different access control approach. Section 3.3 thereafter discusses the consequences of a zero-software TCB that excludes the OS kernel and explains how this requires reconsidering traditional OS concepts. This section thus contextualises the goal for this master's thesis: providing secure resource sharing for embedded PMAs without introducing an omnipotent trusted kernel software layer. Section 3.4 finally concludes.

#### 3.1 Sancus

The previous chapter already mentioned the Sancus platform [40] as a hardware-only PMA implementation that is explicitly targeted at low-end extensible devices. Sancus extends the memory access model and instruction set of a TI MSP430 microcontroller to provide hardware-enforced memory isolation guarantees for Sancus Modules (SMs). Note that an SM is a realisation of the abstract concept of a Self-Protecting Module (SPM), as introduced in Sect. 2.2.1. Therefore, everything presented here for SMs can also be mapped on the more generic concept of SPMs.

The work presented in this master's thesis is built upon Sancus for two major reasons. First, Sancus is an active research project at KU Leuven and its source code is publicly available [39], allowing for extensibility where needed. Second, Sancus features unique caller authentication hardware instructions that will prove essential for this master's thesis.

The following provides a detailed overview of the Sancus system and its internals.

#### 3.1.1 Attacker Model

Sancus protects the internal state of SMs against a powerful attacker which may deploy or tamper with any software running on the node. More specifically, an attacker can address the whole single-address-space, but Sancus' modified memory access logic may disallow access to protected memory depending on the current value of the program counter. An attacker may control all unprotected code, for example the node's OS or shared libraries such as libc. Since SMs do not necessarily have to trust each other, Sancus also protects against an attacker that can deploy arbitrary malicious SMs on the node. Finally, an attacker may control the communication channel between the node and the software provider.

Sancus does not protect against hardware-level attacks however. An attacker with physical access to the node may for example extract memory content via a cold-boot attack [25]. Sancus, like other PMAs, does also not protect SMs against implementation vulnerabilities in their own code section, as previously discussed in Sect. 2.2.2.

#### 3.1.2 Dynamic Deployment Model and Key Management

Sancus is especially interesting for small devices that feature extensibility with software modules from multiple inter-untrustworthy stakeholders. In such a system, adequate isolation of SMs in the shared address space is indeed essential. Sancus supports a generic multiple stakeholder model where an infrastructure provider IP governs a number of low-end computing devices, referred to as nodes  $N_i$ . External software providers  $SP_j$  that are recognised by IP may deploy software modules  $SM_{i,k}$  on the nodes.

Sancus allows a secure mutually authenticated communication channel between SMs running on the same node and between an SM and its remote software provider. To this end, Sancus features hardware extensions and a key derivation scheme to establish a symmetric cryptographic key that is shared by an SM and its software provider SP. The infrastructure provide IP acts as a trusted party that shares a symmetric key  $K_N$  with each of its administered nodes. To make sure the node's key  $K_N$  is kept secret at all time,  $K_N$  is exclusively managed by hardware on the Sancus-enabled node. IP uses its copy of  $K_N$  and a non-secret key derivation function kdf to generate a new key for each software provider, identified by a non-secret SP identifier:

$$K_{N,SP} = kdf(K_N, SP) \tag{3.1}$$

IP distributes these keys to the corresponding software providers. In the end, the software provides want to share a symmetric key with the SMs they deploy on IP's nodes. To so, they need to know the module's *identity*, consisting of (i) the module's code section, and (ii) the load addresses of the code and data sections. An SM's identity may not be known until after the module is loaded in a dynamic deployment

scenario. In such a case, untrusted software running on the node may simply send a symbol table containing the load addresses to the software provider. Provided with  $SM_{identity}$  and  $K_{N,SP}$ , the software provider generates a module-specific key:

$$K_{N,SP,SM} = kdf(K_{N,SP}, SM_{identity})$$

(3.2)

It follows from Eqs. (3.1) and (3.2) that provided with the non-secret SP and  $SM_{identity}$  information and the secret  $K_N$  key, a hardware implementation of the kdf function can calculate the module-specific key on the node as follows:

$$K_{N,SP,SM} = kdf(kdf(K_N, SP), SM_{identity})$$

(3.3)

Sancus-enabled nodes stores one such key for each SM in a protected storage area that is only indirectly accessible through hardware instructions. Since  $K_{N,SP,SM}$  depends on the identity of the corresponding SM, the load process should not be trusted. That is, if the load process changes the content of the code section before enabling protection or sends false load addresses to the software provider, the node's hardware and the software provider won't share a symmetric key. This follows from the fact that a software provider knows the content of the code section of the SM it deploys and combines this with the load addresses to generate his key  $K_{N,SP,SM}$  according to Eq. (3.2). This key will differ from the hardware-generated key  $K_{N,SP,SM}$  of Eq. (3.3) if either the content of the code section or the load addresses differ. As explained further on, the module-specific key  $K_{N,SP,SM}$  can therefore safely be used for local or remote authentication.

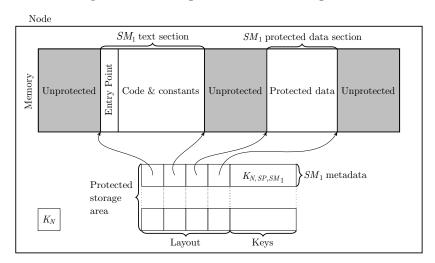

#### 3.1.3 Sancus Module Isolation

As discussed in Sect. 2.2.2, PMAs offer two basic security guarantees towards SMs: entry point restriction and secrecy of the private data section. Sancus implements entry point restriction in hardware by enforcing program flow can only enter an SM through the start address of its corresponding code section, referred to as the physical entry point. Section 3.1.7 explains how SMs employ this single physical entry point for private call stack switching and multiplexing of multiple logical entry points. Sancus furthermore implements program counter based memory isolation by means of a custom Memory Access Logic (MAL) hardware circuit for every SM. These circuits use simple combinational logic to ensure that the private data section of an SM is only accessible when the current value of the program counter lies within the bounds of its corresponding code section. The layout information of an SM (i.e. start and end addresses of the code and data sections) is stored in dedicated registers of a protected storage area that is only accessible from hardware. The use of parallel combinational hardware circuits ensures that the modified memory access semantics are enforced without increasing memory access time. The maximum number of SMs is imposed at hardware synthesisation time, since Sancus needs one MAL circuit per SM.

After loading an SM's code section in memory, a programmer can use the sancus\_enable hardware instruction to enable memory protection for the SM. This

instruction requires the SM's layout as an argument, i.e. the start and end addresses of the module's code and data sections. After verifying that the provided address ranges do not overlap with existing SMs, the instruction stores them in the protected storage area to instantiate a new MAL circuit. The sancus\_enable instruction furthermore requires the software provider's SP identifier as an argument so that it can generate the module-specific key  $K_{N,SP,SM}$  according to Eq. (3.3). This key is stored in the protected storage are as well and may be used by other hardware instructions. Recall from the above that the hardware-generated key will differ from the one of the software provider if an attacker tampers with the module before enabling protection. Finally, the sancus\_enable instruction zeroes out the content of the private data section to make sure an attacker does not have any influence on the initial state of a module. The sancus\_enable instruction returns a status flag to indicate whether the call was successful. Figure 3.1 provides a graphical representation of the protected storage area after enabling a module  $SM_1$ .

FIGURE 3.1: Layout of a Sancus module  $SM_1$  in the shared address space and protected storage area (from [40])

Since SMs can choose their own layout (on a first-come, first-served basis), Sancus' generic memory protection scheme can be used to secure Memory-Mapped I/O (MMIO) peripherals that are being accessed through the memory address space. It suffices indeed to include the relevant MMIO addresses in the private data section of an SM to provide it with exclusive access to the device. There is one pitfall however: the MAL circuits presented above currently only allow a single contiguous private data section per SM. This implies that a module including a MMIO address range in its private data section, cannot at the same time store protected data. Moreover, as it cannot safely provide the call stack needed by higher level programming languages, its corresponding code section should be entirely implemented in assembly. These limitations call for small dedicated driver SMs that restrict access to MMIO peripherals, as illustrated in the next chapter.

A programmer can use the sancus\_disable instruction to disable memory pro-

tection for the currently executing SM, if any. This instruction clears the corresponding entry in the protected storage area and disables the MAL circuit. An SM should clear any remaining secrets in its private data section itself before calling the sancus\_disable instruction.

When one of the MAL circuits detect a memory access violation, a non-maskable interrupt is generated. On such an interrupt, the hardware jumps to the address of the Interrupt Service Routine (ISR) that is registered in the corresponding entry of the interrupt vector table (which is at a fixed location in the TI MSP430's memory). Since the currently executing program performed an illegal memory access, it cannot be continued normally and the ISR typically halts the system. Remark that Sancus currently offers no availability guarantees whatsoever, an attacker or buggy SM can for example perform an illegal memory access to halt the system or execute an infinite loop to monopolise CPU time.

#### 3.1.4 Secure Linking

Sancus features a strong authentication mechanism that allows a module  $SM_1$  to reliably call another module  $SM_2$  running on the same node. More specifically,  $SM_1$  can be ensured before calling  $SM_2$  that (i) protection has been correctly set up for  $SM_2$  as explained above, and (ii) the code section of  $SM_2$  has not been tampered with. To this end, Sancus offers a sancus\_verify\_address instruction that requires two arguments: the expected address of  $SM_2$  and a MAC of the identity of  $SM_2$  calculated with the module-specific key of  $SM_1$ . Since the software provider of  $SM_1$  knows its module-specific key, it can supply  $SM_1$  with the MACs of all the SMs it needs to call, either at deployment time or at run time (to be explained below). The sancus\_verify\_address instruction first verifies whether an SM is currently loaded at the expected address. If this is the case, the instruction computes the MAC of that module using the module-specific key of the calling SM. Finally, the instruction compares the provided MAC with the computed MAC and returns zero if they are not equal.

Since calculating a MAC is an expensive operation for a microcontroller, Sancus includes an optimisation scheme for subsequent authentications. When successfully enabling isolation for a new SM as discussed above, the processor associates it with a non-zero sequential smID that is exclusively managed by hardware. The hardware implementation ensures that smIDs are not re-used before resetting the platform. That is, smIDs uniquely identify an SM within one boot cycle. A programmer can retrieve smIDs using the sancus\_get\_id instruction. This instruction takes an address as an argument and returns the smID of the module loaded at that address, or zero if no module is enabled at the provided address. The sancus\_verify\_address instruction returns the smID of the verified module on successful MAC comparison. The caller may store this smID to simplify subsequent authentications. It indeed

<sup>&</sup>lt;sup>1</sup>Note that the initial Sancus architecture, as presented in [40], simply performed a platform reset on a memory access violation. The explanation of the interrupt mechanism described here is based on personal communication with Job Noorman.

suffices to compare the stored smID with the result of the sancus\_get\_id instruction to ensure that the callee module is still loaded at the expected address.

After successfully verifying  $SM_2$  as above,  $SM_1$  can pass any arguments for the call through CPU registers to guarantee confidentiality and integrity of the data, as explained in Sect. 2.2.2.

#### 3.1.5 Caller Authentication

The above secure linking features provide a caller with guarantees about the state and identity of the module that it is about to call. Sancus can also provide a callee with similar guarantees about its caller.<sup>2</sup> To so, Sancus offers the sancus\_verify\_caller instruction that calculates a MAC of the identity of the calling module and compares it with the expected MAC that is provided as an argument. The hardware logic thereby defines the calling module as the previously executing module and provides the sancus\_get\_caller\_id instruction to retrieve its smid. Like the secure linking instructions from the previous section, the caller authentication instructions are inherently unforgeable as they are entirely implemented in hardware. Two SMs can therefore efficiently establish a mutually authenticated communication channel without trusting any software.

None of the PMAs discussed in Sect. 2.2.3 provides authentication features as strong or efficient as those of Sancus. Strackx et al. [49] propose an approach to set up a mutually authenticated communication channel without using explicit caller authentication hardware instructions. As explained in Sect. 2.2.2 they use the provided return continuation point to identify and verify the module where execution will continue. Their approach thus guarantees information is returned to the correct module, but cannot reliably identify the originator of the message. An attacker may indeed provide an arbitrary return address if he is interested in effect only. The initial Sancus architecture [40] as well as Trustlite [30] therefore employ a three way handshake protocol to set up a true mutually authenticated communication channel without hardware support for caller authentication. First, the calling module  $SM_1$ verifies the module  $SM_2$  it is about to call, using the techniques from the previous section. Next,  $SM_1$  jumps to the physical entry point of  $SM_2$ , passing (i) a secret nonce, and (ii) the address of its own physical entry point as parameters.  $SM_2$  then uses the techniques from the previous section to verify the module corresponding to the provided address and on success calls back to  $SM_1$ , passing the secret nonce as an argument.  $SM_1$  finally responds to  $SM_2$  that it has indeed called  $SM_2$  with that nonce.  $SM_2$  may now safely accept the call. Needless to say that, compared to the simple sancus\_verify\_caller and sancus\_get\_caller\_id instructions presented above, such a three way handshake procedure imposes a serious overhead.

As explained further on, the work presented in this master's thesis relies heavily on Sancus' efficient and reliable caller authentication mechanism.

<sup>&</sup>lt;sup>2</sup>Sancus' caller authentication features are recent work and therefore not discussed in [40]. The explanation provided here is based on personal communication with Job Noorman.

#### 3.1.6 Remote Attestation

Sancus allows a remote software provider to (i) verify that its module has been deployed correctly, and (ii) communicate securely with that module, preserving confidentiality, integrity and authentication over an untrusted communication channel.<sup>3</sup> The basis for these security guarantees lies in the fact that an SM that was correctly loaded shares a secret cryptographic key with its software provider, as explained in Sect. 3.1.2. Sancus thus offers two more instructions that operate on the key of the currently executing module. The sancus\_wrap instruction calculates the MAC of a given message and encrypts its content, whereas the sancus\_unwrap instruction verifies the given MAC of a given message and decrypts its content on success. Since Sancus enforces that a module can only indirectly access its own key via dedicated hardware instructions, a software provider is guaranteed that the message was produced by a specific module that is running uncompromised.

Table 3.1 summarises all the introduced hardware instructions and lists their arguments and return values. The instructions that are marked in the "Crypto" column are slower since they use cryptographic primitives, as explained above.

| Instruction           | Crypto       | Arguments                   | Return Value          |

|-----------------------|--------------|-----------------------------|-----------------------|

| sancus_enable         | $\checkmark$ | SM layout and SP identifier | Success bool          |

| sancus_disable        | -            | -                           | -                     |

| sancus_verify_address | $\checkmark$ | Address and expected MAC    | smID                  |

| sancus_verify_caller  | $\checkmark$ | Expected MAC                | $\operatorname{smID}$ |

| sancus_get_id         | -            | Address                     | $\operatorname{smID}$ |

| sancus_get_caller_id  | -            | -                           | $\operatorname{smID}$ |

| sancus_wrap           | $\checkmark$ | Memory pointers             | Success bool          |

| sancus_unwrap         | $\checkmark$ | Memory pointers             | Success bool          |

Table 3.1: Overview of Sancus' extended instruction set

#### 3.1.7 Sancus Module Entry and Exit Protocol

A programmer can use the extended instruction set from Table 3.1 to securely write his own SMs in assembly code. That is, all the above security guarantees (memory isolation, secure linking, caller authentication and secure communication) can be accomplished with a zero-software TCB. Sancus also comes with a dedicated C compiler to allow the development of SMs in a higher level language on top of the basic PMA hardware. The compiler reduces SM creation to simple annotation of the C code with SM\_ENTRY, SM\_FUNC and SM\_DATA attributes. This section explains how the compiler takes care of low-level things to ensure that SMs represent an isolated execution environment.

<sup>&</sup>lt;sup>3</sup>Note that the initial Sancus architecture presented in [40] only ensured integrity and authentication through a hardware-computed MAC of the passed data. The instructions presented in this section also preserve confidentiality and represent recent work on Sancus. The explanation is therefore based on personal communication with Job Noorman.

As explained in Sect. 2.2.2, SMs should maintain their own private call stack to ensure their internal execution cannot be influenced from the outside. When switching protection domains, the compiler should make sure that (i) the private call stacks are properly saved/restored, and (ii) all unused CPU registers are cleared to avoid private data leakage. To this end, the compiler generates short assembly code stubs that are executed whenever a module is entered or exited.<sup>4</sup> These stubs, referred to as respectively sm\_entry and sm\_exit, are inserted into the code section of every SM. The following paragraphs elaborate on their responsibilities.

Entering a Module Recall from Sect. 3.1.3 that SMs have a single physical entry point at the start of their code section. By inserting the sm\_entry stub at the physical entry point, the compiler can make sure that the stub is executed whenever the SM is entered. This allows the sm\_entry stub to restore the private call stack. The compiler reserves protected memory for the call stack and allocates a fixed location in the private data section to store the stack pointer. Since the private data section is zeroed out on sancus\_enable, the base address of the stack is stored at a fixed location in the text section. This allows the sm\_entry stub to initialise the stack pointer after the module was successfully enabled.

The sm\_entry stub can also be used to forward multiple logical entry points through the single physical entry point. To do so, the Sancus compiler assigns a logical eIDX identifier to each function annotated with SM\_ENTRY and generates a private jump table for each SM. When calling a module, the eIDX of the desired logical entry point should be provided in an agreed register. The sm\_entry stub then simply indexes in its jump table with the provided eIDX to retrieve the internal function address. After calling an external function, a module can be re-entered by supplying a special eIDX value, analogous to the approach described in Sect. 2.2.2.

To successfully call an SM, one should jump to its physical entry point, providing all arguments in agreed CPU registers. The  $sm_entry$  stub expects three kinds of arguments. The first two – the eidx identifier and the address where execution should be continued after calling this module – are supplied through fixed caller-saved registers. Moreover, the  $sm_entry$  stub will forward any arguments intended for the logical entry function, according to normal function calling conventions. The MSP430 architecture uses four 16 bit registers R15 to R12 for function arguments [52], which limits the maximum amount of information to be securely passed for one function call to 64 bits. One may encrypt additional data, store the cypher text in unprotected memory and pass the encryption key securely through the CPU registers.

Exiting a Module The compiler also generates an sm\_exit stub that will be executed whenever a module calls an external function. This stub will first store the internal execution context (program counter, values of CPU registers) on the

<sup>&</sup>lt;sup>4</sup>Note that the Sancus paper [40] does not explain these stubs in great detail. They are relevant however for the work on secure scheduling, presented in Chapter 5. The explanation provided here is therefore partly based on the source code, which can be found at [39] (files sm\_entry.s and sm\_exit.s in sancus-compiler/src/stubs/).

private call stack. Next, it clears all unused CPU registers to avoid leaking of internal private data (i.e. only registers that hold an argument value for the callee are not cleared). The sm\_exit stub thereafter stores the private call stack pointer in a fixed location in the private data section, so that the sm\_entry stub can restore the stack on re-entry. Finally, the sm\_exit stub calls the external module, according the calling conventions explained in the previous paragraph.

When calling an external function the <code>sm\_exit</code> stub passes the address of the physical entry point of its own module as the return address argument. On re-entry, as detected by the special eIDX logical entry index, the <code>sm\_entry</code> stub simply restores the private call stack and continues internal execution.

#### 3.2 Trustlite

This section briefly compares the Sancus [40] architecture presented above with Trustlite [30], a similar hardware-level PMA for embedded devices.

#### 3.2.1 Overview

Like Sancus, Trustlite is explicitly targeted at small embedded devices without hardware support for virtual memory or processor privilege levels. Trustlite's attacker model is similar to that of Sancus too: attackers may control all unprotected code and may deploy additional modules of their choice, but do not have physical access to the node.

SMs are called *trustlets* in Trustlite and represent isolated execution environments in the shared address space. Trustlets are provided with the typical PMA security guarantees from Sect. 2.2.2: they can only be entered from a few predefined entry points and can be provided with exclusive access to their private data section. Moreover, trustlets running on the same node can inspect each others state and set up a mutually authenticated communication channel.

The Trustlite architecture also features a modified hardware exception engine. In short, this secure exception engine stores the execution context of a trustlet on the corresponding private call stack before jumping to the untrusted ISR. This ensures that even in the presence of interrupts, a trustlet solely depends on hardware for integrity and confidentiality of its internal state. Such a set-up allows an untrusted preemptive scheduler to schedule trustlets in between normal unprotected tasks. Section 5.1.2 discusses Trustlite's task model in more detail.

#### 3.2.2 Execution-Aware Memory Protection Unit

The main difference between Trustlite and Sancus is how they enforce the program counter based memory access control rules. Recall from Sect. 3.1.3 that Sancus employs a dedicated MAL hardware circuit per SM to enforce memory isolation. Trustlite on the other hand features an Execution-Aware Memory Protection Unit (EA-MPU). Such an EA-MPU allows to program access control rules in a dedicated fixed-sized hardware table. An entry in this table looks as follows:

(subject address range, object address range, r/w/x permissions)

The hardware logic verifies on every memory access whether the address being accessed is part of an object range. If so, it uses the value of the current program counter to identify the subject performing the memory access and its corresponding access rights on the object. Recall that Sancus' hardware logic provides the code section of an SM with exclusive access to a single contiguous data section. Trustlite's EA-MPU table on the other hand can encode more complex policies. Think for example about multiple non-contiguous private data sections per trustlet or protected shared memory between trustlets. Such flexibility is however hard-limited by the number of entries in the EA-MPU table, which is defined at hardware synthesisation time.